**Instruction Manual**

# Tektronix

TMS 871 1394 Bus Support Package 071-0637-00

There are no current European directives that apply to this product. This product provides cable and test lead connections to a test object of electronic measuring and test equipment.

#### Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to all safety summaries prior to performing service. Copyright © Tektronix, Inc. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software – Restricted Rights clause at FAR 52.227-19, as applicable.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Tektronix, Inc., P.O. Box 1000, Wilsonville, OR 97070-1000

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### SOFTWARE WARRANTY

Tektronix warrants that the media on which this software product is furnished and the encoding of the programs on the media will be free from defects in materials and workmanship for a period of three (3) years from the date of shipment. If a medium or encoding proves defective during the warranty period, Tektronix will provide a replacement in exchange for the defective medium. Except as to the media on which this software product is furnished, this software product is provided "as is" without warranty of any kind, either express or implied. Tektronix does not warrant that the functions contained in this software product will meet Customer's requirements or that the operation of the programs will be uninterrupted or error-free.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period. If Tektronix is unable to provide a replacement that is free from defects in materials and workmanship within a reasonable time thereafter, Customer may terminate the license for this software product and return this software product and any associated materials for credit or refund.

THIS WARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPLACE DEFECTIVE MEDIA OR REFUND CUSTOMER'S PAYMENT IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

#### HARDWARE WARRANTY

Tektronix warrants that the products that it manufactures and sells will be free from defects in materials and workmanship for a period of one (1) year from the date of shipment. If a product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; c) to repair any damage or malfunction caused by the use of non-Tektronix supplies; or d) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

## **Table of Contents**

|                         | Preface                                                                    | ix         |

|-------------------------|----------------------------------------------------------------------------|------------|

|                         | Manual Conventions                                                         | ix         |

|                         | Logic Analyzer Documentation                                               | ix         |

|                         | Contacting Tektronix                                                       | Х          |

| Getting Started         |                                                                            |            |

|                         | Support Description                                                        | 1–2        |

|                         | Logic Analyzer Software Compatibility                                      | 1-2        |

|                         | Standard Accessories                                                       | 1-2        |

|                         | Options                                                                    | 1-2        |

|                         | Requirements and Restrictions                                              | 1–3<br>1–3 |

| <b>Operating Basics</b> |                                                                            | 15         |

| Operating Dasies        |                                                                            |            |

|                         | Setting Up the Support                                                     | 2–1        |

|                         | Channel Group Definitions                                                  | 2-1        |

|                         | Symbols                                                                    | 2-2        |

|                         | Acquiring and Viewing Data                                                 | 2–7        |

|                         | Acquiring Data                                                             | 2-7        |

|                         | Trigger Setups                                                             | 2–7        |

|                         | Custom Clocking                                                            | 2–9        |

|                         | Display Options                                                            | 2-10       |

|                         | Displaying Data                                                            | 2–11       |

|                         | 1394 Bus Packets                                                           | 2–16       |

| Specifications          |                                                                            |            |

|                         | Probe Adapter Description                                                  | 3–1        |

|                         | Probe Adapter Functions                                                    | 3–2        |

|                         | Specifications                                                             | 3-2        |

|                         | Channel Assignments                                                        | 3-4        |

|                         | Signal Descriptions                                                        | 3–9        |

| Functional Verification | on                                                                         |            |

|                         | Functional Verification                                                    | 4–1        |

|                         | Probe Adapter Circuit Description                                          | 4-1        |

|                         | Equipment Required                                                         | 4–1        |

|                         | Verifying Clock Activity Using an Oscilloscope                             | 4–2        |

|                         | Verifying Probe Adapter Functionality with the TLA System Activity Monitor | 4–3        |

|                         | Troubleshooting                                                            | 4–4        |

| Replaceable Parts       |                                                                            |            |

|                         | Parts Ordering Information                                                 | 5–1        |

|                         | Using the Replaceable Parts List                                           | 5-1        |

### List of Figures

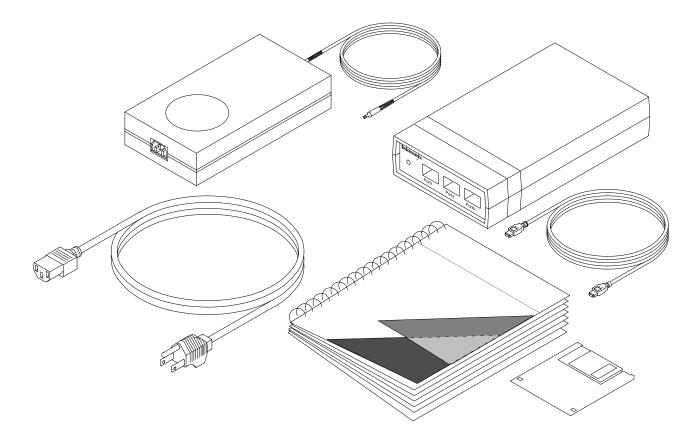

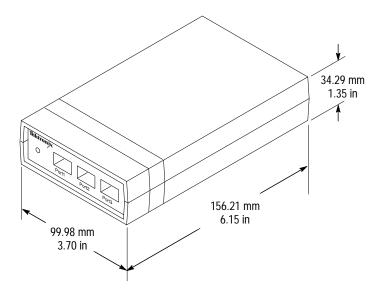

| Figure 1–1: TMS 871 support package                    | 1–1  |

|--------------------------------------------------------|------|

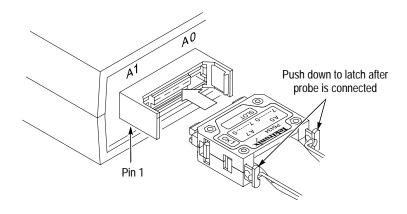

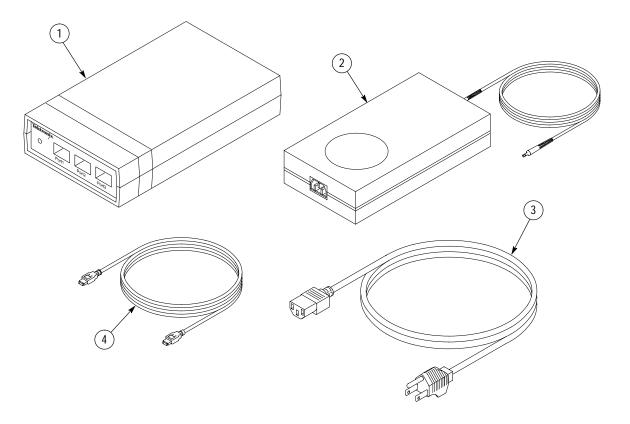

| Figure 1–2: Connecting the cables to the probe adapter | 1–4  |

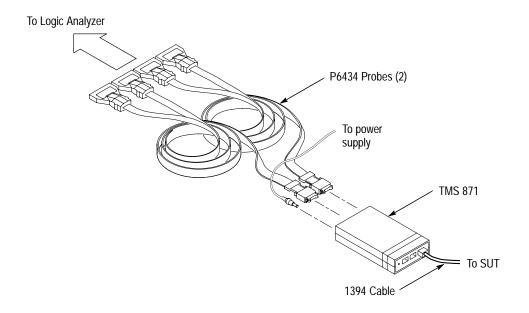

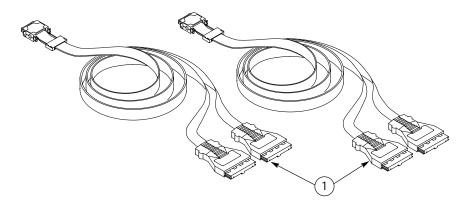

| Figure 1–3: Complete test setup                        | 1–5  |

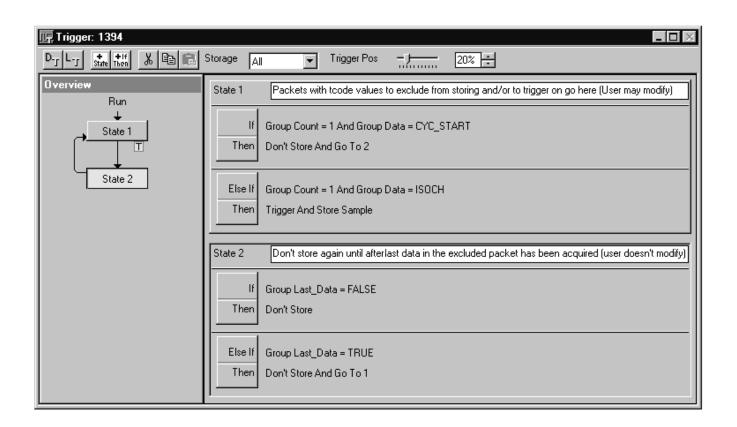

| Figure 2–1: Trigger Setup Window                       | 2–8  |

| Figure 2–2: All Fields Display                         | 2–12 |

| Figure 2–3: Selected Fields Display                    | 2–13 |

| Figure 2–4: Truncated Data in a Selected Field         | 2–14 |

| Figure 2–5: Packet Header Display                      | 2–15 |

| Figure 2–6: Packet Type Display                        | 2–16 |

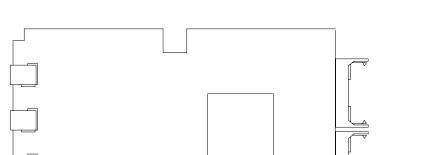

| Figure 3–1: Dimensions of the probe adapter            | 3–3  |

| Figure 4–1: SCLK/2 (system clock) signal test point    | 4–2  |

| Figure 4–2: Activity pattern                           | 4–3  |

|                                                        |      |

### List of Tables

| Table 2–1: Displayed Channel Groups                 | 2–1 |

|-----------------------------------------------------|-----|

| Table 2–2: Error group symbol table definitions     | 2–2 |

| Table 2–3: Event group symbol table definitions     | 2–3 |

| Table 2–4: PCtrl group symbol table definitions     | 2–3 |

| Table 2–5: Speed group symbol table definitions     | 2–4 |

| Table 2–6: Type group symbol table definitions      | 2–4 |

| Table 2–7: Last_Data group symbol table definitions | 2–5 |

| Table 2–8: Tcode group symbol table definitions     | 2–5 |

| Table 3–1: Electrical specifications                | 3–2 |

| Table 3–2: Environmental specifications*            | 3–3 |

| Table 3–3: Certifications and compliances           | 3–3 |

| Table 3-4: Channel group display order              | 3–4 |

| Table 3–5: Quad_Data group assignments              | 3–5 |

| Table 3–6: Speed group assignments                  | 3–6 |

| Table 3–7: Type group assignments                   | 3–6 |

| Table 3–8: Event group assignments                  | 3–6 |

| Table 3–9: Error group assignments                  | 3–7 |

| Table 3–10: Count group assignments                 | 3–7 |

| Table 3–11: Last_Data group assignments             | 3–7 |

| Table 3–12: Phy_Data group assignments              | 3–8 |

| Table 3–13: Phy_Ctrl group assignments              | 3–8 |

| Table 3–14: Clock and qualifier channel assignments | 3–8 |

| Table 3–15: Signal descriptions                     | 3–9 |

| Table 4–1: Equipment list                           | 4–1 |

Table of Contents

# **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it. To avoid potential hazards, use this product only as specified.

Only qualified personnel should perform service procedures.

**To Avoid Fire or Personal Injury Connect and Disconnect Properly.** Connect the probe output to the measurement instrument before connecting the probe to the circuit under test. Disconnect the probe input from the circuit under test before disconnecting the probe from the measurement instrument.

**Observe All Terminal Ratings**. To avoid fire or shock hazard, observe all ratings and marking on the product. Consult the product manual for further ratings information before making connections to the product.

**Do Not Operate With Suspected Failures.** If you suspect there is damage to this product, have it inspected by qualified service personnel.

Do Not Operate in Wet/Damp Conditions.

Do Not Operate in an Explosive Atmosphere.

Keep Product Surfaces Clean and Dry.

**Symbols and Terms** Terms in this Manual. These terms may appear in this manual:

**WARNING**. Warning statements identify conditions or practices that could result in injury or loss of life.

**CAUTION.** Caution statements identify conditions or practices that could result in damage to this product or other property.

Terms on the Product. These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the marking.

WARNING indicates an injury hazard not immediately accessible as you read the marking.

CAUTION indicates a hazard to property including the product.

Symbols on the Product. The following symbols may appear on the product:

CAUTION

Refer to Manual

Protective Ground (Earth) Terminal

Double Insulated

# Service Safety Summary

Only qualified personnel should perform service procedures. Read this *Service Safety Summary* and the *General Safety Summary* before performing any service procedures.

**Do Not Service Alone**. Do not perform internal service or adjustments of this product unless another person capable of rendering first aid and resuscitation is present.

**Disconnect Power**. To avoid electric shock, disconnect the main power by means of the power cord or, if provided, the power switch.

**Use Care When Servicing With Power On**. Dangerous voltages or currents may exist in this product. Disconnect power, remove battery (if applicable), and disconnect test leads before removing protective panels, soldering, or replacing components.

To avoid electric shock, do not touch exposed connections.

### Preface

This instruction manual contains specific information about the TMS 871 1394 Bus support package and is part of a set of information on how to operate this product on compatible Tektronix logic analyzers.

If you are familiar with operating support packages on the logic analyzer for which the TMS 871 1394 Bus support was purchased, you will probably only need this instruction manual to set up and run the support.

If you are not familiar with operating support packages, you will need to supplement this instruction manual with information on basic operations to set up and run the support.

Each logic analyzer has basic information that describes how to perform tasks common to support packages on that platform. This information can be in the form of online help, an installation manual, or a user manual. For complete information on packet types and field descriptions, refer to the *IEEE 1394\_1995 Standard and the IEEE 1394a supplement*.

This manual provides detailed information on the following topics:

- Connecting the logic analyzer to the system under test

- Setting up the logic analyzer to acquire data from the system under test

- Acquiring and viewing data

- Using the probe adapter

#### **Manual Conventions**

This manual uses the following conventions:

- The term "system under test (SUT)" refers to the 1394 Bus system from which data will be acquired.

- The term "logic analyzer" refers to the Tektronix logic analyzer for which this product was purchased.

- The term "module" refers to the Tektronix logic analyzer module for which this product was purchased.

#### Logic Analyzer Documentation

A description of other documentation available for each type of Tektronix logic analyzer is located in the corresponding module user manual. The manual set provides the information necessary to install, operate, maintain, and service the logic analyzer and associated products.

### Contacting Tektronix

| Product<br>Support    | For questions about using Tektronix measurement products, call<br>toll free in North America:<br>1-800-TEK-WIDE (1-800-835-9433 ext. 2400)<br>6:00 a.m. – 5:00 p.m. Pacific time |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | Or contact us by e-mail:<br>tm_app_supp@tek.com                                                                                                                                  |

|                       | For product support outside of North America, contact your local Tektronix distributor or sales office.                                                                          |

| Service<br>Support    | Tektronix offers extended warranty and calibration programs as<br>options on many products. Contact your local Tektronix<br>distributor or sales office.                         |

|                       | For a listing of worldwide service centers, visit our web site.                                                                                                                  |

| For other information | In North America:<br>1-800-TEK-WIDE (1-800-835-9433)<br>An operator will direct your call.                                                                                       |

| To write us           | Tektronix, Inc.<br>P.O. Box 1000<br>Wilsonville, OR 97070-1000<br>USA                                                                                                            |

| Website               | Tektronix.com                                                                                                                                                                    |

|                       |                                                                                                                                                                                  |

## **Getting Started**

This chapter provides information on the following topics and tasks:

- A description of the TMS 871 1394 Bus support package

- Logic analyzer software compatibility

- Options and accessories

- Support restrictions

- How to connect to the system under test

Figure 1–1 shows components of the TMS 871 1394 Bus support package.

Figure 1–1: TMS 871 support package

### **Support Description**

The TMS 871 1394 Bus support package displays data from the IEEE 1394 High Performance Serial Bus. The support runs on a compatible Tektronix logic analyzer equipped with a 68-channel or wider module, and requires two P6434 probes.

A complete list of standard and optional accessories is provided at the end of the parts list in the *Replaceable Mechanical Parts* chapter.

#### Logic Analyzer Software Compatibility

The TMS 871 application software requires Version 3.0 and higher of TLA 700 System software running on the logic analyzer, and Version 3.0 and higher of TLA 700 LA module firmware on the modules you will be using.

#### **Standard Accessories**

The probe adapter is shipped with the following standard accessories:

- TMS 871 Support SW Disk

- TMS 871 Support Instruction Manual

- 1394 cable

- 5V power supply

- North American power cord

#### **Options**

The following options are available when ordering the TMS 871 Support:

- Option A1 Power Cord, Europe, 230 V

- Option A2 Power Cord, United Kingdom, 230 V

- Option A3 Power Cord, Australia, 230 V

- Option A5 Power Cord, Switzerland, 230 V

- Option 21 Add 2 P6434 Probes

#### **Requirements and Restrictions**

|                    | You should review the general requirements and restrictions of 1394 Bus supportion in the information on basic operations.                                                                                                                                                    |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                    | You should also review electrical, environmental, and mechanical specifications<br>in the <i>Specifications</i> chapter in this manual as they pertain to your system under<br>test, as well as the following descriptions of other support requirements and<br>restrictions. |  |

| System Clock Rate  | The TMS 871 support package can acquire data from the 1394 bus operating at speeds of 100, 200, or 400 Mb/s.                                                                                                                                                                  |  |

| Merged Module Pair | If you have a pair of modules that are merged in the logic analyzer, you can<br>un-merge them (and use either one). If you want the modules to remain merged,<br>then the probe adapter must connect to the master module.                                                    |  |

### **Connecting to a System Under Test**

To connect the logic analyzer to the probe adapter, follow these steps:

**CAUTION**. Static discharge can damage the probe adapter, the probes, or the module. To prevent static damage, handle all of these products only in a static-free environment.

- 1. Plug the power supply into an appropriate power source.

- **2.** Connect the DC plug to the probe adapter to provide power to the probe adapter.

- **3.** Connect the P6434 probes to the 1394 probe adapter. Align the probe tip with the mating connector and gently connect as shown in Figure 1–2.

Figure 1-2: Connecting the cables to the probe adapter

**CAUTION.** Incorrect handling of the P6434 probe while connecting it to the probe adapter can result in damage to the probe or to the mating connector on the probe adapter. To avoid damaging the probe and probe adapter, always position the probe perpendicular to the mating connector and gently connect the probe.

**4.** Connect the module ends of the P6434 probes to the corresponding connectors on the logic analyzer. The probe module ends are keyed.

**NOTE**. The right-side P6434 probe (as seen from the rear of the probe adapter) connects to D1–D0 and C3–C2 connectors on the logic analyzer. This may not match the color coding on a pre-labeled P6434 probe.

- 5. Connect the 1394 probe adapter to the 1394 system under test using the 6-pin 1394 cable supplied with the probe adapter, or any standard 6-pin 1394 cable. Use any of the three ports on the front of the probe adapter.

- 6. The complete test setup appears in Figure 1-3 on page 1-5.

Figure 1–3: Complete test setup

Getting Started

# Setting Up the Support

This section describes how to set up the support and includes these topics:

- Channel group definitions

- Symbol table files

Remember that the information in this section is specific to the operations and functions of the TMS 871 support package. Information on basic operations describes general tasks and functions.

Before you acquire and display data, you need to load the support and specify setups for clocking and triggering as described in the information on basic operations. The support provides default values for each of these setups, but you can change them as needed.

#### **Channel Group Definitions**

The software automatically defines channel groups for the support.

**Channel Groups** The defined channel groups are Data, Speed, Type, Event, Error, Count, Last\_Data, Phy\_Data, and Phy\_Ctrl.

To see which signal is in which channel group, refer to the channel group assignment tables beginning on page 2–2. Tables 2–2 through 2–6 show the channel assignments for the setup.

| Table 2–1: Displayed Channel Groups |

|-------------------------------------|

|-------------------------------------|

| Group name | Display radix                                |

|------------|----------------------------------------------|

| Data       | HEX                                          |

| Mnemonic   | NONE (disassembly text generated by support) |

| Speed      | SYM                                          |

| Туре       | SYM <sup>1</sup>                             |

| Event      | SYM <sup>1</sup>                             |

| Error      | SYM <sup>1</sup>                             |

| Count      | DEC                                          |

| Last_Data  | SYM <sup>1</sup>                             |

| Phy_Data   | HEX <sup>1</sup>                             |

| Phy_Ctrl   | SYM <sup>1</sup>                             |

| Timestamp  |                                              |

<sup>1</sup> These groups are acquired but not displayed in a default listing. They may be added to the listing window by the user.

### **Symbols**

The TMS 871 support supplies the following seven symbol table files:

- 1394\_Error.tsf

- 1394\_Event.tsf

- 1394\_PCtrl.tsf

- 1394\_Speed.tsf

- 1394\_Type.tsf

- 1394\_Last.tsf

- 1394\_Tcode.tsf

Each file replaces specific channel group values with symbolic values when Symbolic is the radix for the channel group.

**Error Group** The symbol table file for the Error group is 1394\_Error.

The error group represents hardware errors that can occur on the bus. The symbol table shows the error code for the corresponding signal that was set. Multiple errors are not covered by the table.

Table 2–2 shows the 1394\_Error symbol table.

|            | Error group value                                                                               |                                                |

|------------|-------------------------------------------------------------------------------------------------|------------------------------------------------|

| Symbol     | Iso_Cycle_Lost<br>Cyc_Too_Long<br>State_Timeout<br>Quad_Align_Err<br>Ack_Err<br>Self_Packet_Err | Description                                    |

|            | 0 0 0 0 0 0                                                                                     | No Error                                       |

| ISO_LOST   | 1 0 0 0 0 0                                                                                     | Isochronous cycle did not complete             |

| ISO_LONG   | 0 1 0 0 0 0                                                                                     | Isochronous cycle exceeds maximum time         |

| TIMEOUT    | 0 0 1 0 0 0                                                                                     | Phy stayed in one state too long               |

| ALIGN_ERR  | 0 0 0 1 0 0                                                                                     | Quad data not ending on quadlet boundary       |

| ACK_ERR    | 0 0 0 0 1 0                                                                                     | 2nd nibble of ACK not logical inverse          |

| SLFPKT_ERR | 0 0 0 0 0 1                                                                                     | 2nd quadlet of self-ID pkt not logical inverse |

**Event Group** The symbol table file for the Event group is 1394\_Event.

The event group collects the validation strobe that, with SysClk, determine the packet is valid. The events are grouped for displaying added information in the listing and for triggering use.

Table 2–3 shows the 1394\_Event symbol table.

|          | Event group value                                               |                            |

|----------|-----------------------------------------------------------------|----------------------------|

| Symbol   | Arb_Gap<br>Sub_Gap<br>Data_Rdy<br>Ack_Rcvd<br>Reset<br>HW_Error | Description                |

|          | 0 0 0 0 0 0                                                     | No event                   |

| ARB_GAP  | 1 0 0 0 0 0                                                     | Arbitration gap detected   |

| SUB_GAP  | 0 1 0 0 0 0                                                     | Subaction gap detected     |

| DATA_RDY | 0 0 1 0 0 0                                                     | Quadlet data is valid      |

| ACK_RCVD | 0 0 0 1 0 0                                                     | Acknowledge data is valid  |

| HW_ERROR | 0 0 0 0 1 0                                                     | Hardware error has occured |

| RESET    | X X X X X 1                                                     | Bus reset detected         |

Table 2–3: Event group symbol table definitions

**PCtrl Group** The symbol table file for the PCtrl group is 1394\_PCtrl.

The PCtrl group represents the PHY CTL signals as defined by 1394a. This group is not normally displayed. The information is for those advanced users who wish to look at the signals immediately available at the PHY-Link interface.

Table 2–4 shows the 1394\_PCtrl symbol table.

|         | PCtrl group value        |                                 |

|---------|--------------------------|---------------------------------|

| Symbol  | Phy_Ctrl_0<br>Phy_Ctrl_1 | Description                     |

| IDLE    | 0 0                      | No activity                     |

| STATUS  | 1 0                      | PHY sending status info to link |

| RECEIVE | 0 1                      | Packets being received          |

| GRANT   | 0 0                      | PHY granting bus to link        |

**Speed Group** The symbol table file for the Speed group is 1394\_Speed.

The speed group indicates the bus speed as 100, 200, or 400 Mb/s.

Table 2–5 shows the 1394\_Speed symbol table.

|       | Speed group value  |                   |

|-------|--------------------|-------------------|

| Value | Speed_0<br>Speed_1 | Description       |

| 100   | 0 0                | Speed is 100 Mb/s |

| 200   | 1 0                | Speed is 200 Mb/s |

| 400   | 0 1                | Speed is 400 Mb/s |

| _     | 1 1                | Undefined         |

Table 2–5: Speed group symbol table definitions

**Type Group** The symbol table file for the Type group is 1394\_Type.

The type group represents a collection of special packet identification signals.

Table 2–6 shows the 1394\_Type symbol table.

|        | Type group value                          |                    |

|--------|-------------------------------------------|--------------------|

| Symbol | Bcast_Packet<br>Self_Id_Packet<br>Iso_Cyc | Description        |

|        | 0 0 0                                     | Other packet type  |

| BCAST  | 1 X X                                     | Broadcast packet   |

| SLFID  | X 1 X                                     | Self-Id packet     |

| ISO    | X X 1                                     | Isochronous packet |

**Last\_Data Group** The symbol table file for the Last\_Data group is 1394\_Last.

The Last\_Data symbols label the one bit (last data quadlet in a packet) as true or false to clarify usage in Trigger Setups.

Table 2–7 shows the 1394\_Last symbol table.

#### Table 2–7: Last\_Data group symbol table definitions

| Value | Last_Rx_Data |

|-------|--------------|

| True  | 1            |

| False | 0            |

**Tcode Group** The symbol table file for the Tcode group is 1394\_Tcode. It is used for trigger setup to identify transaction codes in the Data group on the first quadlet of a packet.

Table 2–8 shows the 1394\_Tcode symbol table.

|              | Tcode group value |                                |

|--------------|-------------------|--------------------------------|

| Symbol       | Tcode             | Description                    |

| WR_REQ_QUAD  | X X X X X X 0 X   | Write Request for Data Quadlet |

| WR_REQ_BLK   | XXXXXX1X          | Write Request for Data Block   |

| WR_RESP      | X X X X X X 2 X   | Write Response                 |

| RD_REQ_QUAD  | X X X X X X 4 X   | Read Request for Data Quadlet  |

| RD_REQ_BLK   | X X X X X X 5 X   | Read Request for Data Block    |

| RD_RESP_QUAD | X X X X X X 6 X   | Read Request for Data Quadlet  |

| RD_RESP_BLK  | X X X X X X 7 X   | Read Response for Data Block   |

| CYC_START    | X X X X X X 8 X   | Cycle Start                    |

| LOCK_REQ     | X X X X X X 9 X   | Lock Request                   |

| ISOCH        | XXXXXXAX          | Isochronous or Streaming Data  |

| LOCK_RESP    | XXXXXXBX          | Lock Response                  |

Table 2–8: Tcode group symbol table definitions

Information on basic operations describes how to modify an existing symbol table, create new symbol tables, and use symbolic values for triggering and displaying other channel groups symbolically, such as the Address channel group.

## **Acquiring and Viewing Data**

This section describes how to acquire data and view it in a listing window with the following topics and tasks:

- Acquiring data

- Trigger setups

- Clocking options

- Display options

- Displaying data

#### **Acquiring Data**

Once you load the 1394 setup, you can specify the trigger, choose a clocking mode, and acquire data.

If you have any problems acquiring data, refer to information on basic operations in your online help.

#### **Trigger Setups**

The signals available on the 1394 bus allow for many triggering possibilities. The .tla files include trigger setting examples, which will be similar to the example shown in Figure 2–1 on page 2–8.

#### Figure 2–1: Trigger Setup Window

This trigger/capture state machine model can be used for a wide variety of situations. In this example, the default is to store everything with the State 1 being used to identify certain packet types by a specific tcode bit pattern in the first quadlet of the packet. The Last\_Data group is TRUE only on the last quadlet which allows State 2 to exclude (not store) the entire packet identified in State 1. In this example, all Cycle Start packets are excluded from being stored and the logic analyzer is triggered on an Isochronous packet.

Note that the custom clocking options also allow the user to not store long packet data, gaps, and errors. As there is a limit to the number of clauses in a trigger state (typically 4), the custom clocking option should be examined for more complex triggering/storage situations.

Using the model shown in Figure 2–1, some variations useful to 1394 might be:

- Group Speed (symbolic). Can exclude packets labeled with a speed code. For example, all 100Mb/s packets can be excluded. State 2 is not needed.

- Group Event (symbolic for event). Singles out specific types of qualifying events. Overlaps custom clocking for gaps and errors. Useful for identifying trigger point, such as triggering on a bus reset.

- Group Count>n. Can be used to store only the first n bytes of the packet.

State 2 is not needed. Note that this is covered for a value of 16 by a custom clocking option.

- Type (symbolic for type). Allows broadcast, self-id packets, or iso packets to be excluded. For more information, refer to Tables 3–7 and 3–13 on pages 3–6 and 3–8 for a description of the signals in this group. State 2 is not needed.

- Group Count=1 and Group Data=(symbolic for tcode). Allows various packet types to be excluded from storage. Used with State 2.

- Group Error=(symbolic for error). Singles out a specific type of error to not store or to trigger on. State 2 is not needed.

- Group Count=n and Group Data=HEX. Generic way to specify a packet by information known to be in a certain byte. For example, the destination address which is the first 16 bytes of the first quadlet for several different packet types. Used with State 2 to exclude capture from the identified quadlet through the end of the packet.

### **Custom Clocking**

The TMS 871 will add the selection 1394 to the Load Support Package dialog box, under the File pulldown menu. Once the 1394 support has been loaded, the Custom clocking mode selection in the logic analyzer Setup menu is also enabled. Custom will be the default selection whenever the 1394 support has been loaded.

When Custom is selected, the TMS 871 support will modify the Custom Clocking Options menu to display three options:

- Clocking Mode

- Quadlet Capture

- Packet Truncation

The selections for these three options are defined below.

**Clocking Mode** The Clocking Mode option allows the user to select either Normal or Raw Phy modes of clocking. Normal mode is used for disassembly and for all groups except Phy\_Data and Phy\_Ctrl. In Normal mode, different clock options are available.

Raw Phy mode clocks at twice the rate of Normal mode (the Phy-Link SCLK signal rate) and is used for acquiring the low-level Phy\_Ctrl and Phy\_Data group signals only. Because of the different clocking, other group values may or may

not be valid when acquired. Raw Phy mode is not useful for disassembly. When this mode is selected, the settings of the other two clocking options have no effect.

**Quadlet Capture** There are four quadlet capture selections possible, listed below. These only take effect when the Clocking Mode is set to Normal. The All Valid selection is the default.

- All Valid. The all valid selection qualifies quadlets for acquisition by looking for a Data\_Rdy, Arb\_Gap, Sub\_Gap, Ack\_Rcvd, HW\_Error, or Reset signal in the Event group (see Table 3–8 on page 3–6). This selection captures all the valid quadlets which include gaps, acks, and errors.

- All Valid, no gaps. Same as All Valid except Arb\_Gap and Sub\_Gap events are not captured.

- All Valid, no errors. Same as All Valid except errors (HW\_errors) are not captured.

- All Valid, no gaps or errors. Same as All Valid except no gaps or errors are captured.

## Packet TruncationThere are two selections possible here: None and After 16 quadlets. None is the<br/>default. These only take effect when the Clocking Mode is set to Normal.

- None. There is no attempt to truncate packets.

- After 16 quadlets. Only quadlets up to and including the 16th quadlet in each packet will be captured in this mode.

#### **Display Options**

The TMS 871 disassembles the fields of the packets specified in 1394-1995 and 1394a standards. The TMS 871 displays various levels of packet detail as selected by choosing one of five disassembly modes as described in *Displaying Data* on page 2–11.

### **Displaying Data**

There are six formats to display 1394 bus cycles:

- Waveform (Timing)

- Listing (State):

- All Fields

- Selected Fields

- Truncated Data

- Packet Header

- Packet Type

All Listing modes are available through the Disassembly Properties menu of the Listing display.

All Fields All captured data (packet data, packet header, gaps, errors, and ack data) will be displayed in this mode. Refer to Figure 2–2 on page 2–12.

All numeric values in the 1394 Mnemonics column are in hexadecimal, unless otherwise specified.

| Sample     | 1394<br>Data         | 1394<br>Mnemonics |                             | 1394<br>Speed | 1394<br>Count    | Timestamp                |

|------------|----------------------|-------------------|-----------------------------|---------------|------------------|--------------------------|

| 219        | FFFFFFF              | 01E4:             | FFFFFFF                     | 100           | 31               | 325.500 ns               |

| 220        | 4DDA5418             | data_CRC:         | 4DDA5418                    | 100           | 31               | 326.000 ns               |

| 221        |                      | Subaction Gap     |                             | 100           | 31               | 7.731,500 us             |

| 222        |                      | Arbitration Gap   |                             | 100           | 31               | 7.405,000 us             |

| 223        | FFFF008F             | CYCLE START       |                             | 100           | 1                | 67.058,000 us            |

|            | FFFF008F             | dest_ID:          | FFFF(Local Bus, Bdcst Node) | 100           | 1                | r                        |

|            | FFFF008F             | tl:               | 0                           | 100           | 1                |                          |

|            | FFFF008F             | rt:               | 0 (retry_1)                 | 100           | 1                |                          |

|            | FFFF008F             | tcode:            | 8                           | 100           | 1                |                          |

|            | FFFF008F             | pri:              | F                           | 100           | 1                |                          |

| 224        | FFC1FFFF             | source_ID:        | FFC1(Local Bus, Node 01)    | 100           | 23               | 325.500 ns               |

| 225        | F0000200             | dest_offset:      | FFFF F0000200               | 100           | 3                | 326.000 ns               |

| 226        | 6F3D1028             | cycle_time:       | 6F3D1028                    | 100           | 4                | 325.500 ns               |

| 227        | 00578D84             | header_CRC:       | 00578D84                    | 100           | 5                | 325.500 ns               |

| 228        | 01E87FA0             | ISOCH STREAM DAT  |                             | 100           | 1                | 1.139,000 us             |

|            | 01E87FA0             | data_length:      | 1E8 (488 decimal)           | 100           | 1                |                          |

|            | 01E87FA0             | tag:              | 1                           | 100           | 1                |                          |

|            | 01E87FA0             | channel:          | 3F (63 decimal)             | 100           | 1                |                          |

|            | 01E87FA0             | tcode:            | A                           | 100           | 1                |                          |

|            | 01E87FA0             | sy:               | 0                           | 100           | 1                |                          |

| 229        | 762784F4             | headerCRC:        | 762784F4                    | 100           | 23               | 326.000 ns               |

| 230        | 0178002F             | 0000:             | 0178002F                    | 100           | 3                | 325.000 ns               |

| 231        | 8000FFFF             | 0004:             | 8000FFFF                    | 100           | 4<br>5<br>6<br>7 | 325.500 ns               |

| 232        | 788700FF             | 0008:             | 788700FF                    | 100           | 5                | 326.000 ns               |

| 233        | FFFFFFF              | 0000:             | FFFFFFF                     | 100           | 6                | 325.500 ns               |

| 234        | 00000000             | 0010:             | 0000000                     | 100           |                  | 325.500 ns               |

| 235        | 00000000             | 0014:             | 0000000                     | 100           | 8                | 325.500 ns               |

| 236        | 00000000             | 0018:             | 0000000                     | 100           | .9               | 325.500 ns               |

| 237        | 00000000             | 0010:             | 0000000                     | 100           | 10               | 325.500 ns               |

| 238        | 00000000             | 0020:             | 0000000                     | 100           | 11               | 325.500 ns               |

| 239        | 00000000             | 0024:             | 0000000                     | 100           | 12               | 325.500 ns               |

| 240        | 00000000             | 0028:             | 0000000                     | 100           | 13               | 325.500 ns               |

| 241        | 00000000             | 0020:             | 0000000                     | 100<br>100    | 14<br>15         | 325.500 ns               |

| 242<br>243 | 00000000             | 0030:             | 00000000<br>00000000        | 100           | 16               | 326.000 ns<br>325.000 ns |

| 243        | 000000000            | 0034:             |                             | 100           | 16               | 325.000 Hs<br>325.500 Hs |

| 244        | 00000000             | 0030:             | 00000000<br>00000000        | 100           | 18               | 326.000 ns               |

| 245        | 00000000             | 0040:             | 00000000                    | 100           | 19               | 325.000 ns               |

| 246        | 00000000             | 0040:             | 00000000                    | 100           | 20               | 326.000 ns               |

| 247<br>248 | 00000000             | 0044:             | 00000000                    | 100           | 20               | 325.500 ns               |

| 240        | 000000000            | 0040:             | 00000000                    | 100           | 22               | 325.500 ris              |

| 249        | 000000000            | 00401             | 00000000                    | 100           | 23               | 325.500 ris              |

| 250        | 00000000             | 0054:             | 00000000                    | 100           | 24               | 325.500 ris              |

| 252        | 94870008             | 0058:             | 94870008                    | 100           | 25               | 325.500 ris              |

| 252        | 94370008<br>9A130910 | 0050:             | 94370003<br>9A130910        | 100           | 26               | 326.000 ns               |

| 253        | 4D24E034             | 0060:             | 4D24E034                    | 100           | 27               | 325.000 ns               |

| 204        | 40242034             | 00001             | 10212037                    | 100           |                  | 525.000 HS               |

Figure 2–2: All Fields Display

#### **Selected Fields**

In this mode, only the most significant packet header data fields will be displayed and/or disassembled, along with all data. Gaps will not be displayed, nor will header or data CRC's. Ack data and errors will be displayed. Refer to Figure 2–3.

| Sample | 1394<br>Data | 1394<br>Mnemonics |                                         | 1394<br>Speed | 1394<br>Count | Timestamp     |

|--------|--------------|-------------------|-----------------------------------------|---------------|---------------|---------------|

| 223    | FFFF008F     | CYCLE START       |                                         | 100           | 1             | 82.520,500 us |

|        | FFFF008F     | dest_ID:          | FFFF(Local Bus, Bdcst Node)             | 100           | 1             | 02.520,500 us |

|        | FFFF008F     | tl:               | 0                                       | 100           | 1             |               |

|        | FFFF008F     | rt:               | 0 (retry 1)                             | 100           | 1             |               |

| 224    | FFC1FFFF     | source_ID:        | 0 (retry_1)<br>FFC1(Local Bus, Node 01) | 100           | 1<br>1<br>2   | 325.500 ns    |

| 226    | 6F3D1028     | cycle_time:       | 6F3D1028                                | 100           | 4             | 651.500 ns    |

| 228    | 01E87FA0     | ISOCH STREAM DAT  |                                         | 100           | 1             | 1.464,500 us  |

| 220    | 01E87FA0     | data_length:      | 1E8 (488 decimal)                       | 100           | ī             | 11101,500 45  |

|        | 01E87FA0     | tag:              | 1                                       | 100           | 1             |               |

|        | 01E87FA0     | channel:          | 3F (63 decimal)                         | 100           | 1             |               |

|        | 01E87FA0     | sy:               | 0                                       | 100           | 1 1           |               |

| 230    | 0178002F     | 0000:             | 0178002F                                | 100           | 1<br>1<br>3   | 651.000 ns    |

| 231    | 8000FFFF     | 0004:             | 8000FFFF                                | 100           |               | 325.500 ns    |

| 232    | 788700FF     | 0008:             | 788700FF                                | 100           |               | 326.000 ns    |

| 233    | FFFFFFF      | 00000:            | FFFFFFF                                 | 100           | ā l           | 325.500 ns    |

| 234    | 00000000     | 0010:             | 0000000                                 | 100           | 5<br>6<br>7   | 325.500 ns    |

| 235    | 00000000     | 0014:             | 0000000                                 | 100           | i s           | 325.500 ns    |

| 236    | 00000000     | 0018:             | 0000000                                 | 100           | 8             | 325.500 ns    |

| 237    | 00000000     | 0010:             | 0000000                                 | 100           | 10            | 325.500 ns    |

| 238    | 00000000     | 0020:             | 0000000                                 | 100           | 11            | 325.500 ns    |

| 239    | 00000000     | 0024:             | 0000000                                 | 100           | 12            | 325.500 ns    |

| 240    | 00000000     | 0028:             | 0000000                                 | 100           | 13            | 325.500 ns    |

| 241    | 00000000     | 0020:             | 0000000                                 | 100           | 14            | 325.500 ns    |

| 242    | 00000000     | 0030:             | 0000000                                 | 100           | 15            | 326.000 ns    |

| 243    | 00000000     | 0034:             | 0000000                                 | 100           | 16            | 325.000 ns    |

| 244    | 00000000     | 0038:             | 0000000                                 | 100           | 17            | 325.500 ns    |

| 245    | 00000000     | 0030:             | 0000000                                 | 100           | 18            | 326.000 ns    |

| 246    | 00000000     | 0040:             | 0000000                                 | 100           | 19            | 325.000 ns    |

| 247    | 00000000     | 0044:             | 0000000                                 | 100           | 20            | 326.000 ns    |

| 248    | 00000000     | 0048:             | 0000000                                 | 100           | 21            | 325.500 ns    |

| 249    | 00000000     | 0040:             | 0000000                                 | 100           | 22            | 325.500 ns    |

| 250    | 00000000     | 0050:             | 0000000                                 | 100           | 23            | 325.500 ns    |

| 251    | 00000000     | 0054:             | 0000000                                 | 100           | 24            | 325.500 ns    |

| 252    | 94870008     | 0058:             | 94870008                                | 100           | 25            | 325.500 ns    |

| 253    | 9A130910     | 0050:             | 9A130910                                | 100           | 26            | 326.000 ns    |

| 254    | 4D24E034     | 0060:             | 4D24E034                                | 100           | 27            | 325.000 ns    |

| 255    | BC711EE0     | 0064:             | BC711EEO                                | 100           | 28            | 326.000 ns    |

| 256    | F6C19B14     | 0068:             | F6C19B14                                | 100           | 29            | 325.500 ns    |

| 257    | B256A6A8     | 0060:             | B256A6A8                                | 100           | 30            | 325.500 ns    |

| 258    | 2A1D483C     | 0070:             | 2A1D483C                                | 100           | 31            | 325.500 ns    |

| 259    | 77E00788     | 0074:             | 77E00788                                | 100           | 31            | 325.500 ns    |

Figure 2-3: Selected Fields Display

## **Truncated Data** This mode displays selected fields, but only the first 16 data quadlets of any data field. Refer to Figure 2–4.

| Sample     | 1394<br>Data                            | 1394<br>Mnemonics |                             |            | 1394<br>Count    | Timestamp                               |

|------------|-----------------------------------------|-------------------|-----------------------------|------------|------------------|-----------------------------------------|

| 223        | FFFF008F                                | CYCLE START       |                             | 100        | 1                | 117.351,000 us                          |

|            | FFFF008F                                | dest_ID:          | FFFF(Local Bus, Bdcst Node) | 100        | 1                | , , , , , , , , , , , , , , , , , , , , |

|            | FFFF008F                                | tl:               | 0                           | 100        |                  |                                         |

|            | FFFF008F                                | rt:               | 0 (retry_1)                 | 100        | 1<br>1<br>2      |                                         |

| 224        | FFC1FFFF                                | source_ID:        | FFC1(Local Bus, Node 01)    | 100        | 2                | 325.500 ns                              |

| 226        | 6F3D1028                                | cycle_time:       | 6F3D1028                    | 100        | 4                | 651.500 ns                              |

| 228        | 01E87FA0                                | ISOCH STREAM DAT  |                             | 100        | 1                | 1.464,500 us                            |

|            | 01E87FA0                                | data_length:      | 1E8 (488 decimal)           | 100        | 1                |                                         |

|            | 01E87FA0                                | tag:              | 1                           | 100        | 1                |                                         |

|            | 01E87FA0                                | channel:          | 3F (63 decimal)             | 100        | 1                |                                         |

|            | 01E87FA0                                | sy:               | 0                           | 100        | 1                |                                         |

| 230        | 0178002F                                | 0000:             | 0178002F                    | 100        | 1113456789       | 651.000 ns                              |

| 231        | 8000FFFF                                | 0004:             | 8000FFFF                    | 100        | 4                | 325.500 ns                              |

| 232        | 788700FF                                | 0008:             | 788700FF                    | 100        | 5                | 326.000 ns                              |

| 233        | FFFFFFF                                 | 0000:             | FFFFFFF                     | 100        | 6                | 325.500 ns                              |

| 234        | 00000000                                | 0010:             | 0000000                     | 100        | 7                | 325.500 ns                              |

| 235        | 00000000                                | 0014:             | 0000000                     | 100        | 8                | 325.500 ns                              |

| 236        | 00000000                                | 0018:             | 0000000                     | 100        |                  | 325.500 ns                              |

| 237        | 00000000                                | 0010:             | 0000000                     | 100        | 10               | 325.500 ns                              |

| 238        | 00000000                                | 0020:             | 0000000                     | 100        | 11               | 325.500 ns                              |

| 239<br>240 | 000000000000000000000000000000000000000 | 0024:<br>0028:    | 00000000                    | 100<br>100 | 12<br>13         | 325.500 ns<br>325.500 ns                |

| 240<br>241 | 000000000                               | 0028:             | 00000000                    | 100        | 14               | 325.500 hs                              |

| 241        | 000000000                               | 0030:             | 00000000                    | 100        | 14               | 325.500 ns                              |

| 242        | 000000000                               | 0034:             | 00000000                    | 100        | 16               | 325.000 ns                              |

| 243        | 000000000                               | 0038:             | 00000000                    | 100        | 17               | 325.000 ns                              |

| 355        | FFFF008F                                | CYCLE START       | 0000000                     | 100        |                  | 117.352,000 us                          |

| 555        | FFFF008F                                | dest_ID:          | FFFF(Local Bus, Bdcst Node) | 100        | 1<br>1<br>1<br>2 | 117.552,000 us                          |

|            | FFFF008F                                | tl:               | 0                           | 100        | 1                |                                         |

|            | FFFF008F                                | rt:               | 0 (retry_1)                 | 100        | 1                |                                         |

| 356        | FFC1FFFF                                | source_ID:        | FFC1(Local Bus, Node 01)    | 100        | 5                | 325.500 ns                              |

| 358        | 6F3D2028                                | cycle_time:       | 6F3D2028                    | 100        | 4                | 651.000 ns                              |

| 360        | 01E87FA0                                | ISOCH STREAM DAT  |                             | 100        |                  | 1.465,000 us                            |

|            | 01E87FA0                                | data_length:      | 1E8 (488 decimal)           | 100        | 1<br>1<br>1<br>1 |                                         |

|            | 01E87FA0                                | tag:              | 1                           | 100        | - ī              |                                         |

|            | 01E87FA0                                | channel:          | 3F (63 decimal)             | 100        | 1                |                                         |

|            | 01E87FA0                                | sy:               | 0                           | 100        | 1                |                                         |

Figure 2-4: Truncated Data in a Selected Field

**Packet Header** This mode displays the selected header fields, without data quadlets. Refer to Figure 2–5.

| Sample     |                      | 1394<br>Mnemonics               |                                          |            | 1394<br>Count | Timestamp                |

|------------|----------------------|---------------------------------|------------------------------------------|------------|---------------|--------------------------|

| 223        | FFFF008F             | CYCLE START                     |                                          | 100        | 1             | 122.559,000 us           |

|            | FFFF008F             | dest_ID:                        | FFFF(Local Bus, Bdcst Node)              | 100        | 1             | · · ·                    |

|            | FFFF008F             | tl:                             | 0                                        | 100        | 1             |                          |

|            | FFFF008F             | rt:                             | 0 (retry_1)                              | 100        | 1             |                          |

| 224        | FFC1FFFF             | source_ID:                      | FFC1(Local Bus, Node 01)                 | 100        | 2             | 325.500 ns               |

| 226        | 6F3D1028             | cycle_time:                     | 6F3D1028                                 | 100        | 4             | 651.500 ns               |

| 228        | 01E87FA0             | ISOCH STREAM DAT                | A                                        | 100        | 1             | 1.464,500 us             |

|            | 01E87FA0             | data_length:                    | 1E8 (488 decimal)                        | 100        | 1             |                          |

|            | 01E87FA0             | tag:                            | 1                                        | 100        | 1             |                          |

|            | 01E87FA0             | channel:                        | 3F (63 decimal)                          | 100        | 1             |                          |

|            | 01E87FA0             | sy:                             | 0                                        | 100        | 1             |                          |

| 355        | FFFF008F             | CYCLE START                     |                                          | 100        | 1             | 122.560,500 us           |

|            | FFFF008F             | dest_ID:                        | FFFF(Local Bus, Bdcst Node)              | 100        | 1             |                          |

|            | FFFF008F             | t]:                             | 0                                        | 100        | 1             |                          |

|            | FFFF008F             | rt:                             | 0 (retry_1)                              | 100        | 1             |                          |

| 356        | FFC1FFFF             | source_ID:                      | FFC1(Local Bus, Node 01)                 | 100        | 2             | 325.500 ns               |

| 358        | 6F3D2028             | cycle_time:                     | 6F3D2028                                 | 100        | 4             | 651.000 ns               |

| 360        | 01E87FA0             | ISOCH STREAM DAT                |                                          | 100        | 1             | 1.465,000 us             |

|            | 01E87FA0             | data_length:                    | 1E8 (488 decimal)                        | 100        | 1             |                          |

|            | 01E87FA0             | tag:                            |                                          | 100        | 1             |                          |

|            | 01E87FA0             | channel:                        | 3F (63 decimal)                          | 100        | 1             |                          |

| 40.7       | 01E87FA0             | sy:                             | 0                                        | 100        | 1             | 4.33 550 500             |

| 487        | FFFF008F             | CYCLE START                     |                                          | 100        | 1             | 122.559,500 us           |

|            | FFFF008F             | dest_ID:                        | FFFF(Local Bus, Bdcst Node)              | 100        | 1             |                          |

|            | FFFF008F             | tl:                             | O (mature 1)                             | 100        | 1             |                          |

| 400        | FFFF008F             | rt:                             | 0 (retry_1)<br>STG1 (here] Dive Node G1) | 100        | 1             | 335 500                  |

| 488        | FFC1FFFF             | source_ID:                      | FFC1(Local Bus, Node 01)                 | 100<br>100 | 2             | 325.500 ns<br>651.000 ns |

| 490<br>492 | 6F3D3028<br>01E87FA0 | cycle_time:<br>ISOCH STREAM DAT | 6F3D3028                                 | 100        | 4             |                          |

| 492        | 01E87FA0             | data_length:                    | 1E8 (488 decimal)                        | 100        | 1             | 1.465,000 us             |

|            | 01E87FA0             | taq:                            | 1 (400 UECIMAL)                          | 100        | 1             |                          |

|            | 01E87FA0             | channel:                        | JF (63 decimal)                          | 100        | 1             |                          |

|            | OTFOLLMO             | criarine :                      | or (os decimar)                          | 1 100      | <u> </u>      |                          |

Figure 2–5: Packet Header Display

## **Packet Type** This mode displays errors and Ack data, but only one line for each packet (packet type) is displayed . Refer to Figure 2–6.

| Sample |          | 1394<br>Mnemonics |         |     | 1394<br>Count | Timestamp      |

|--------|----------|-------------------|---------|-----|---------------|----------------|

| 91     | FFFF008F | CYCLE STAR        | t.      | 100 | 1             | 0 ps           |

| 96     | 01E87FA0 | ISOCH STRE        | AM DATA | 100 | 1             | 2.441,500 us   |

| 223    | FFFF008F | CYCLE STAR        | ιT.     | 100 | 1             | 122.559,000 us |

| 228    | 01E87FA0 | ISOCH STRE        | AM DATA | 100 | 1             | 2.441,500 us   |

| 355    | FFFF008F | CYCLE STAR        | t.      | 100 | 1             | 122.560,500 us |

| 360    | 01E87FA0 | ISOCH STRE        | AM DATA | 100 | 1             | 2.441,500 us   |

| 487    | FFFF008F | CYCLE STAR        | t.      | 100 | 1             | 122.559,500 us |

| 492    | 01E87FA0 | ISOCH STRE        | AM DATA | 100 | 1             | 2.441,500 us   |

Figure 2-6: Packet Type Display

### 1394 Bus Packets

Refer to the *IEEE 1394\_1995 Standard and the IEEE 1394a supplement* for complete information on packet types and field descriptions.

# **Specifications**

This chapter contains the following information:

- Probe adapter description

- Specification tables

- Channel assignment tables

- Signal descriptions

### **Probe Adapter Description**

The probe adapter consists of an enclosed unit with three 6-pin connectors for 1394 Bus connections, and two 34-pin connectors for the LA interconnect (via P6434 probes). Power is provided by an external power supply that plugs into the back of the probe adapter. Signals from the 1394 Bus cable flow into the probe adapter and through the P6434 probes to the logic analyzer.

All probe adapter circuitry is powered from an external power supply which must supply 5-15 volts DC, at 350 milliamps maximum. The adapter has an internal fuse and circuitry which protects against damage from reversed-polarity power supply connections.

The probe adapter contains 3-port, 1394a-compliant PHY circuitry. The probe adapter, following 1394 protocols, causes a bus reset when connected, when it arbitrates for a node on the bus. Once connected, the probe adapter does not generate any traffic from the Link layer, and does not expect any traffic to be addressed to it.

After connecting, the probe adapter monitors all PHY-link data and conditions the data with an on-board FPGA to generate signals for acquisition and triggering by the logic analyzer.

The signals presented by the probe adapter to the logic analyzer are TTL level with a clocking speed of 50 MHz or less. The probe adapter does not cause excessive loading on critical signals.

## **Probe Adapter Functions**

The probe adapter captures the following types of bus packets and events.

- Asynch Quadlet

- Isoch Quadlet

- Self ID Quadlet

- Phy Config Quadlet

- Ack Byte

- Arb Gap

- Sub-Action Gap

- Bus Reset

The following Hardware Errors are detected:

- Isochronous cycle lost

- Isochronous cycle too long

- State timeout

- Quadlet alignment error

- Acknowledge packet error

- Self ID packet error

## **Specifications**

These specifications are for a probe adapter connected between a compatible Tektronix logic analyzer and a 1394-1995 or 1394a-compliant device. The system must be connected in a legal 1394 topology and running at S100, S200, or S400 speeds. Table 3–1 shows the electrical requirements of the probe adapter in order for the support to acquire correct data.

#### Table 3–1: Electrical specifications

| Characteristics                     | Requirements              |

|-------------------------------------|---------------------------|

| Probe Adapter DC power requirements |                           |

| 5 V Vcc Voltage                     | 4.75–5.25 VDC             |

| 5 V Vcc Current                     | I max (calculated) 350 mA |

Table 3–2 shows the environmental specifications.

Table 3–2: Environmental specifications\*

| Characteristic    | Description                        |

|-------------------|------------------------------------|

| Temperature       |                                    |

| Maximum operating | +50° C (+122° F)                   |

| Minimum operating | 10° C (+50° F)                     |

| Non-operating     | -50° C to +75° C (-67° to +167° F) |

\* Designed to meet Tektronix standard 062-2847-00 class 5.

Table 3–3 shows the compliances that apply to the probe adapter.

Table 3–3: Certifications and compliances

| EMC Compliance | Meets the intent of Directive 89/336/EEC for Electromagnetic<br>Compatibility when it is used with the product(s) stated in the<br>specifications table. Refer to the EMC specification published for the<br>stated products. May not meet the intent of the directive if used with<br>other products. |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FCC Compliance | Emissions comply with FCC Code of Federal Regulations 47, Part 15, Subpart B, Class A Limits.                                                                                                                                                                                                          |  |

Figure 3–1 shows the dimensions of the probe adapter.

Figure 3–1: Dimensions of the probe adapter

# **Channel Assignments**

Channel assignments shown in Table 3–5 through Table 3–14 use the following conventions:

- All signals are required by the support unless indicated otherwise.

- Channels are shown starting with the most significant bit (MSB) descending to the least significant bit (LSB). Note that 1394 convention labels the most significant bit as zero.

- Section:channel refers to the module channel number.

The group assignment tables indicate whether the signal is required for custom clocking and/or the disassembly. Required signals must be connected to properly strobe and login bus data into acquisition memory, and to disassemble the acquired bus data.

Channel groups will be displayed in the order shown in Table 3–4.

| Group name | Display radix                                                 |  |

|------------|---------------------------------------------------------------|--|

| Data       | HEX                                                           |  |

| Mnemonic   | None (disassembly text generated by support package software) |  |

| Speed      | SYM                                                           |  |

| Туре       | SYM (default not displayed)                                   |  |

| Event      | SYM (default not displayed)                                   |  |

| Error      | SYM (default not displayed)                                   |  |

| Count      | DEC                                                           |  |

| Last_Data  | SYM (default not displayed)                                   |  |

| Phy_Data   | HEX (default not displayed)                                   |  |

| Phy_Ctrl   | SYM (default not displayed)                                   |  |

| Timestamp  |                                                               |  |

#### Table 3-4: Channel group display order

Table 3–5 shows the probe section and channel assignments for the Quad group and the signal to which each channel connects. By default, this channel group is displayed in hexadecimal.

| Bit order | Section:channel | Signal name | Required for clocking<br>or disassembly |

|-----------|-----------------|-------------|-----------------------------------------|

| 31        | A3:7            | Data_0      | Disassembly                             |

| 30        | A3:6            | Data_1      | Disassembly                             |

| 29        | A3:5            | Data_2      | Disassembly                             |

| 28        | A3:4            | Data_3      | Disassembly                             |

| 27        | A3:3            | Data_4      | Disassembly                             |

| 26        | A3:2            | Data_5      | Disassembly                             |

| 25        | A3:1            | Data_6      | Disassembly                             |

| 24        | A3:0            | Data_7      | Disassembly                             |

| 23        | A2:7            | Data_8      | Disassembly                             |

| 22        | A2:6            | Data_9      | Disassembly                             |

| 21        | A2:5            | Data_10     | Disassembly                             |

| 20        | A2:4            | Data_11     | Disassembly                             |

| 19        | A2:3            | Data_12     | Disassembly                             |

| 18        | A2:2            | Data_13     | Disassembly                             |

| 17        | A2:1            | Data_14     | Disassembly                             |

| 16        | A2:0            | Data_15     | Disassembly                             |

| 15        | A1:7            | Data_16     | Disassembly                             |

| 14        | A1:6            | Data_17     | Disassembly                             |

| 13        | A1:5            | Data_18     | Disassembly                             |

| 12        | A1:4            | Data_19     | Disassembly                             |

| 11        | A1:3            | Data_20     | Disassembly                             |